- ЛОГИЧЕСКИЕ СХЕМЫ

- ЛОГИЧЕСКИЕ СХЕМЫ

-

- физ. устройства, реализующие функции матем. логики. Л. с. подразделяют на 2 класса: комбинационные схемы (Л. с. без памяти) и послед овател ьностные схемы (Л. с. с памятью). Л. с. являются основой любых систем (различных назначений и физ. природы) обработки дискретной информации. Л. с. может быть представлена в виде многополюсника (рис. 1), на к-рый поступает п входных сигналов и с к-рого снимается т выходных сигналов. При этом как независимые (логические) переменные Х 1,......, Х n, так и ф-ции Y1,..., Yn, также наз. логическими, могут принимать к.-л. значения только из одного и того же конечного множества значений.

Наиб. распространены т. н. двоичные Л. с., для к-рых всё множество сигналов ограничено двумя значениями, отмечаемыми символами 1 и 0 и подчиняющимися условию: a=1, если

и а=0, если

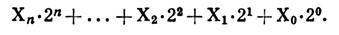

и а=0, если  Для представления чисел с помощью двоичных переменных 0 и 1 чаще всего применяют т. н. позиционный двоичный код, в к-ром разряды двоичного числа расставлены по степеням числа 2:

Для представления чисел с помощью двоичных переменных 0 и 1 чаще всего применяют т. н. позиционный двоичный код, в к-ром разряды двоичного числа расставлены по степеням числа 2:

Напр., двоичное число 11012=1*8+1*4+0*2+1*1 = 13. Поэтому при описании работы Л. с. необходимо различать, выступает данный сигнал в качестве числа или в качестве логич. переменной.

Для описания работы Л. с. используют табличный или аналитич. способы. В первом случае строят т. н. таблицу истинности, в к-рой приводятся все возможные сочетания входных сигналов (аргументов) и соответствующие им значения выходных сигналов (логич. ф-ций). В двоичной логике число разл. сочетаний из п аргументов равно 2n, а число логических ф-ций

Логич. ф-ции одного и двух независимых аргументбв, т. н. элементарные логич. ф-ции, приведены в табл. 1.

Логич. ф-ции одного и двух независимых аргументбв, т. н. элементарные логич. ф-ции, приведены в табл. 1.

Табл. 1

Функции (операции)

Аргументы:

Выражение через 3 осн. операции

Название

логич. ф-ций

X1 0 0 1 1 Х 2 0 1 0 1

0000

константа нуль

0001

конъюнкция (операция И)

0010

запрет по Х 2

0011

тождественность X1

0100

запрет по X1

0101

тождественность X2

0110

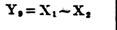

сумма по модулю два

0111

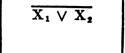

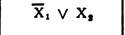

дизъюнкция (операция ИЛИ)

1000

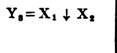

стрелка Пирса (операция ИЛИ -НЕ)

1001

равнозначность

1010

отрицание Х 2 (операция НЕ)

1011

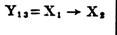

импликация от X2 к X1

1100

отрицание Х 1 (операция НЕ)

1101

импликация от X1 к X2

1110

штрих Шеффера (операция И - НЕ)

1111

константа единица

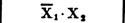

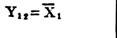

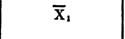

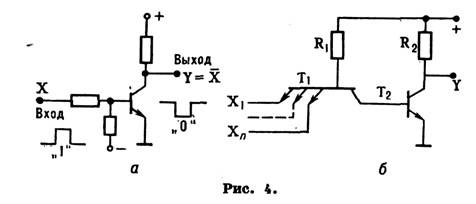

Для всех ф-ций приведены таблицы истинности (столбец 2). При аналитич. описании работы Л. с. используют спец. символы, обозначающие нек-рые логич. операции (столбец 1). Так, черта над переменной обозначает логич. операцию НЕ (логич. отрицание или инверсия), символ

- логич. операцию ИЛИ (логич. сложение или дизъюнкция), символ умножения (точка) - логич. операцию И (логич. умножение или конъюнкция). Три перечисленные ф-ции часто наз. основными, т. к. они в совокупности составляют функционально полную систему, с помощью к-рой можно выразить любую другую логич. ф-цию, как это показано в столбце 3 таблицы. Вообще же функциональной полнотой обладают мн. системы ф-ций, в частности каждая из ф-ций И-НЕ или ИЛИ-НЕ [1].

- логич. операцию ИЛИ (логич. сложение или дизъюнкция), символ умножения (точка) - логич. операцию И (логич. умножение или конъюнкция). Три перечисленные ф-ции часто наз. основными, т. к. они в совокупности составляют функционально полную систему, с помощью к-рой можно выразить любую другую логич. ф-цию, как это показано в столбце 3 таблицы. Вообще же функциональной полнотой обладают мн. системы ф-ций, в частности каждая из ф-ций И-НЕ или ИЛИ-НЕ [1].

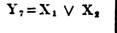

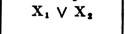

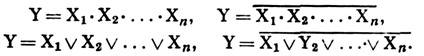

В табл. 1 приведены все ф-ции одного и двух аргументов; нек-рые из этих ф-ций могут быть распространены и на те случаи, когда число переменных больше двух. Напр., справедливы равенства

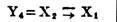

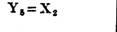

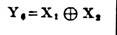

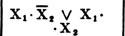

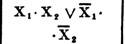

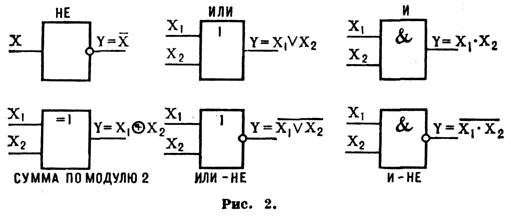

Логические элементы. Л. с., выполняющая одну из элементарных логич. операций, наз. логич. элементом (ЛЭ). ЛЭ имеет один или неск. входов, на к-рые поступают сигналы Xi, и один выход. При этом выходной сигнал Y элемента не должен оказывать обратного воздействия на входной сигнал (однонаправленность ЛЭ). ЛЭ изображают прямоугольником, в верхней части к-рого обозначают символ операции. Входы показывают с левой стороны прямоугольника, выходы с правой. Операцию инверсии отмечают кружком у соответствующего выхода (рис. 2). Л. с. любой сложности можно построить из любого функционально полного набора ЛЭ путём соединения выходов одних элементов со входами других. Напр., для осуществления логич. операции

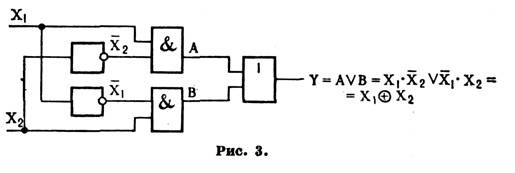

Суммирование по модулю два (строка У 6 в табл. 1) можно собрать схему, состоящую из 5 элементов, выполняющих операции НЕ, ИЛИ и И (рис. 3). К ЛЭ предъявляется комплекс требований, нередко имеющих взаимоисключающий характер, напр. большое быстродействие и малое энергопотребление, высокая надёжность и низкая себестоимость, небольшие габариты и масса и высокая технологичность произ-ва. Из всех возможных разновидностей ЛЭ (электромеха-нич., пневматич., электронных, оптич. и т. п.) совокупности всех требований наилучшим образом удовлетворяют полупроводниковые элементы, т. н. логич. (цифровые) полупроводниковые интегр. микросхемы, ИМС (см. Цифровые устройства,[2]). Простейшим ЛЭ является инвертор, к-рый может быть реализован на однотранзисторном усилит. каскаде, работающем в режиме электронного ключа (рис. 4, а). Если на вход этого усилителя подать достаточно высокое положит. напряжение (логич. сигнал 1), то транзистор откроется и напряжение на его выходе упадёт (логич. сигнал 0). И наоборот, при низком уровне входного сигнала транзистор будет заперт и напряжение на его выходе будет максимальным (логич. сигнал 1). Простейший элемент типа И-НЕ (рис. 4, б )получится при добавлении к инвертору на транзисторе входной логич. схемы И на многоэмиттерном транзисторе Т1. (см. Транзистор биполярный). Если на все входы транзистора Т1. поданы сигналы высокого уровня, то соответствующие базовые переходы Т1. будут закрыты. Тогда ток, протекающий через резистор R1 и два последовательно включённых перехода транзисторов Т1. (база - коллектор) и Т2 (база-эмиттер), открывает выходный транзистор Т 2. Если же на один или несколько входов Xi подано низкое напряжение (логич. 0), то открываются соответствующие переходы эмиттер-база транзистора Т1. При этом практически весь ток, текущий через R1 пойдёт через открытый эмиттерный переход, т. к. его сопротивление значительно меньше сопротивления двух последовательно включённых переходов, и транзистор Т2 окажется запертым. Широкое применение находят и др. типы ИМС. Это вызвано тем, что схемные и технологич. особенности определяют, как минимум, 2 самых важных параметра логич. микросхем: быстродействие и потребляемую мощность (для совр. ЛЭ в интегр. исполнении время переключения из одного состояния в др., т, е. быстродействие ЛЭ, составляет от 50 до 0,2 нc при потребляемой мощности от 0,001 до 40 мВт). Эти параметры противоречивы, и в рамках одной технологии при улучшении одного неизбежно ухудшается другой, в связи с чем общее число типов ИМС, имеющих разл. сочетание осн. параметров и выполненных по разным технологиям, непрерывно расширяется.

Из ЛЭ разл. типа собирают более сложные функционально законченные устройства (операц. элементы, ОЭ), выполняющие определённые (не элементарные) логич. операции над входными сигналами и строящиеся по комбинационной и последовательностной схемам.

Комбинационные схемы - Л. с. без запоминания переменных - схемы, в к-рых в любой момент времени значения выходных сигналов

однозначно определяются значениями входных сигналов Xi. Наиб. распространёнными типами комбинац. схем являются ЛЭ (простейшие комбинац. схемы) и ОЭ след. типов: преобразователи кодов (шифраторы и дешифраторы), коммутаторы (мультиплексоры и демультиплексоры), ариметич. устройства (компараторы, сумматоры и пр.).

однозначно определяются значениями входных сигналов Xi. Наиб. распространёнными типами комбинац. схем являются ЛЭ (простейшие комбинац. схемы) и ОЭ след. типов: преобразователи кодов (шифраторы и дешифраторы), коммутаторы (мультиплексоры и демультиплексоры), ариметич. устройства (компараторы, сумматоры и пр.).

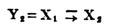

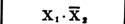

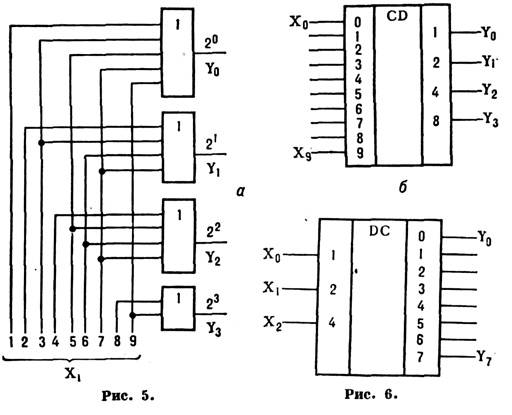

Шифратор (кодировщик) - ОЭ, преобразующий единичный сигнал на одном из п входов в m -разрядный выходной код. Напр., на пульте ввода информации имеется 10 клавиш с номерами i=0,1, ..., 9. При нажатии i -й клавиши на вход шифратора подаётся единичный сигнал Xi. На выходе шифратора должны появиться сигналы, отображающие двоичный код (Y3, . . ., Y0) входного сигнала X/. Как видно из таблицы истинности шифратора (табл. 2), в этом случае нужна комбинац. схема с десятью входами и четырьмя выходами. На выходе Y0 единица появляется при нажатии любой нечётной клавиши, т. е. Y0=

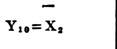

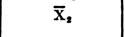

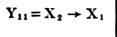

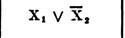

Для остальных выходов логич. ф-ции имеют вид

Для остальных выходов логич. ф-ции имеют вид

Следовательно, для реализации шифратора необходимы четыре элемента ИЛИ: пятивходовый, два четырёхвходовых и двухвходовый. Схема шифратора и его условно-графич. обозначение показаны на рис. 5, а, б.

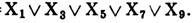

Дешифратор (декодировщик) - ОЭ, преобразующий n -разрядный входной код в сигнал только на одном из своих m выходов. Дешифратор двоичного n -разрядного кода имеет 2n выходов. Таблицу истинности дешифратора, переводящего двоичный код в десятичное число (код "1 из 10"), можно получить из табл. 2, взаимно поменяв в ней местами входные и выходные переменные. По таблице истинности составляются логич. ф-ции и схема дешифратора. условно-графич. обозначения дешифратора трёхразрядного двоичного кода в код "1 из 8" см. на рис. 6.

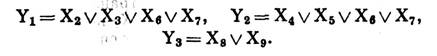

Мультиплексор - ОЭ, осуществляющий адресное переключение заданного числа входных сигналов на один выход. Мультиплексор имеет два вида входов: информационные (Х 0, ..., Х n) и адресные (А 0, ..., А m). Выбор информац. линия производится кодом, поступающим на адресные входы. Поэтому на выход устройства передаются сигналы с того информац. входа Xi, номер к-рого соответствует двоичному коду на адресных входах А т,...., А 0. Схему и условно-графич. обозначение мультиплексора на четыре входа см. на рис. 7. Из схемы следует, что

Для увеличения числа информац. входов необходимо увеличивать число адресных входов, т. к. п=2 т.

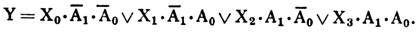

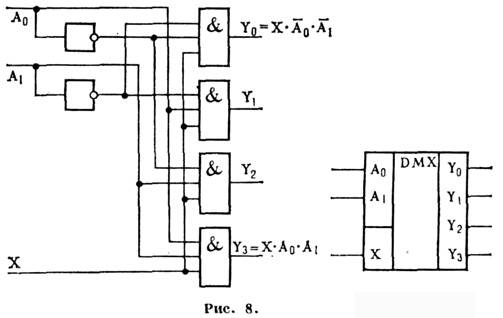

Демультиплексор - ОЭ, осуществляющий адресное подключение одного входного сигнала X к одному из множества выходов Y0, . . ., Yn. Сигнал X, поступающий на информац. вход, передаётся на тот выход Yi, номер к-рого задан адресными сигналами А m, . . ., А 0. Логика выбора адреса в демультиплексоре такая же, как и в мультиплексоре. Схему и условно-графич. обозначение демультиплексора на 4 выхода см. на рис. 8.

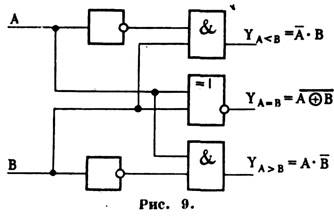

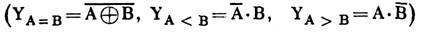

Компаратор - ОЭ, производящий сравнение двух чисел А и В. Результат сравнения отображается единичным логич. уровнем на одном из трёх выходов компаратора YA=B, Y

Y

Y Таблица истинности одноразрядного компаратора весьма проста (табл. 3). По ней легко составить логич. ф-ции

Таблица истинности одноразрядного компаратора весьма проста (табл. 3). По ней легко составить логич. ф-ции

и схему данного устройства (рис. 9).

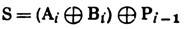

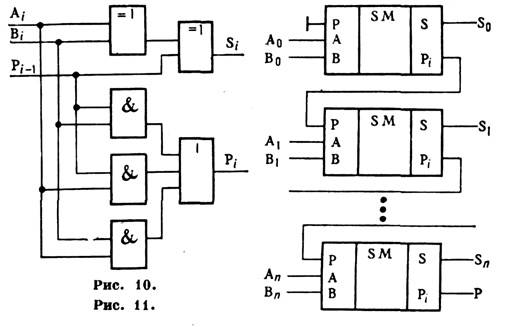

Сумматор - ОЭ, выполняющий операцию сложения неск. чисел. Двоичный сумматор является достаточно универсальным элементом и используется также при выполнении операций вычитания, умножения и деления. При сложении двух многоразрядных двоичных чисел в каждом i -м разряде находится сумма трёх чисел по модулю два (А i, В i) и переноса, поступившего из младшего разряда - Pi-1), и формируется сигнал переноса в старший разряд - Р i. По таблице истинности одноразрядного сумматора (табл. 4) составляют логич. ф-ции для выходных величин:

и

и

По этим ф-циям строят схему сумматора (рис. 10) на двух элементах СУММА ПО МОДУЛЮ 2, трёх элементах И и одном элементе ИЛИ. Для сложения многоразрядных чисел используют многоразрядные сумматоры, к-рые в простейшем случае получают последоват. соединением одноразрядных сумматоров (рис. 11).

Таб л. 2

Входы (десятичное число Xi)

Выходы (двоичный

код)

Y3

Y2

Y1

Y0

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

Табл. 3

Входы

Выходы

А

В

YA = B

YA<B

YA>B

0

0

1

0

0

0

1

0

1

0

1

0

0

0

1

1

1

1

0

0

Табл. 4

Входы

Выходы

слагаемые

перенос

сумма

перенос

А i

в i

Pi-l

Si

Р i

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

1

1

0

1

0

1

1

1

1

1

1

Рассмотренный способ реализации разл. комбинац. схем на основе ЛЭ не является единственно возможным.

Для этих же целей можно использовать и постоянные запоминающие устройства (ПЗУ), в к-рых записаны необходимые таблицы истинности. При этом роль адреса, выбираемого из ПЗУ слова, будут играть входные сигналы (аргументы), а роль реализуемой логич. ф-ции - слово, записанное в ПЗУ по этому адресу.

Последовательностные схемы - Л. с. с запоминанием переменных - схемы, выходные сигналы к-рых зависят не только от значения входных сигналов в данный момент времени, но и от последовательности значений входных сигналов в предшествующие моменты времени. Последовательностные схемы собираются из комбинационных путём введения в них обратных связей. Простейшим последовательностным устройством является RS-триггер, наз. также базовым элементом последовательностной логики. Базовые элементы лежат в основе всех остальных устройств последовательностной логики: многофункциональных триггеров разл. типа, регистров, счётчиков, многих видов запоминающих устройств.

Работу последовательностных схем обычно рассматривают в дискретном времени, состоящем из отд. интервалов - тактов. Длительность отд. тактов несущественна, при этом они могут быть как равными, так и различными. Изменение выходных сигналов последо-вательностного устройства может происходить только в начале (или конце) нового такта. В обозначения входных и выходных сигналов помимо их номера может включаться и обозначение номера такта; так

и

и  означают выходной сигнал Yi в п- мтакте и в следующем, (n+1)-м, такте. Последовательностные схемы обычно описывают при помощи таблиц переключений или переключат. ф-ций, представляющих собой таблицы истинности и логич. ф-ции, составленные с учётом номера такта. При описании таких схем используют также и временные диаграммы.

означают выходной сигнал Yi в п- мтакте и в следующем, (n+1)-м, такте. Последовательностные схемы обычно описывают при помощи таблиц переключений или переключат. ф-ций, представляющих собой таблицы истинности и логич. ф-ции, составленные с учётом номера такта. При описании таких схем используют также и временные диаграммы.

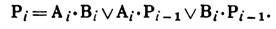

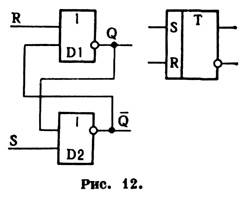

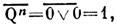

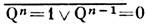

Триггеры -Последовательностные элементы с двумя устойчивыми выходными состояниями (0 или 1). Под действием входных сигналов триггер способен переключаться в др. состояние с противоположным выходным сигналом. Осн. назначение - запоминание двоичной информации, заключающееся в сохранении триггером заданного состояния после прекращения действия переключающего сигнала. Простейший RS-триггер представляет собой устройство из двух ЛЭ D1 и D2 типа ИЛИ-НЕ (или И-НЕ), охваченных перекрёстной положительной обратной связью (рис. 12). Он имеет два свободных (управляющих) входа, обычно обозначаемых буквами R (от англ. reset - возврат) и S (англ. set - установка), и два выхода: прямой (Q) и инверсный

Состояние триггера определяется по сигналам на его прямом выходе, т. е. считают, что триггер находится в единичном состоянии, если 0 = 1 и

Состояние триггера определяется по сигналам на его прямом выходе, т. е. считают, что триггер находится в единичном состоянии, если 0 = 1 и  и в нулевом состоянии, если Q=0 и

и в нулевом состоянии, если Q=0 и  Как видно из схемы рис. 12, состояние триггера может быть определено из логич. ф-ций элементов ИЛИ-НЕ: Q

Как видно из схемы рис. 12, состояние триггера может быть определено из логич. ф-ций элементов ИЛИ-НЕ: Q  (для D1) и

(для D1) и  =

= (для D2). Анализ состояния триггера в каждом из п тактов необходимо начинать с того элемента (D1или D2), на управляющем входе к-рого появилась 1. В этом случае, независимо от сигнала на 2-м входе этого элемента - выходного сигнала др. элемента в конце предыдущего, ( п-1)-го такта,- на его выходе возникнет 0. Сигнал логич. О по цепи обратной связи поступает на др. элемент и совместно со вторым управляющим сигналом определяет его выходное состояние. Всего возможны четыре комбинации управляющих сигналов:

(для D2). Анализ состояния триггера в каждом из п тактов необходимо начинать с того элемента (D1или D2), на управляющем входе к-рого появилась 1. В этом случае, независимо от сигнала на 2-м входе этого элемента - выходного сигнала др. элемента в конце предыдущего, ( п-1)-го такта,- на его выходе возникнет 0. Сигнал логич. О по цепи обратной связи поступает на др. элемент и совместно со вторым управляющим сигналом определяет его выходное состояние. Всего возможны четыре комбинации управляющих сигналов:

R = l и S=0, тогда

и

и  т. е. происходит установка триггера в нулевое устойчивое состояние (Q "=0 и

т. е. происходит установка триггера в нулевое устойчивое состояние (Q "=0 и  независимо от состояния триггера в предыдущем, ( п-1)-м такте;

независимо от состояния триггера в предыдущем, ( п-1)-м такте;

R=0 и S=1, тогда

Qn=0

Qn=0 0=1, т. е. триггер устанавливается в единичное устойчивое состояние независимо от предыдущего состояния;

0=1, т. е. триггер устанавливается в единичное устойчивое состояние независимо от предыдущего состояния;

R = S=0, тогда

и

и

т. е. состояние триггера в n -м такте осталось таким же, как и в предыдущем, ( п-1)-м, такте;

т. е. состояние триггера в n -м такте осталось таким же, как и в предыдущем, ( п-1)-м, такте;

R=S = 1, тогда Qn=

и

и  т. е. оба выходных сигнала равны 0, что не позволяет однозначно определить состояние системы.

т. е. оба выходных сигнала равны 0, что не позволяет однозначно определить состояние системы.

Комбинации управляющих сигналов определяют и соответствующие режимы работы триггера: режим записи 0 (режим возврата), режим записи единицы (режим установки), режим хранения информации Qn = Qn-1 и запрещённый (неоднозначный) режим

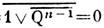

Переход RS -триггера из одного режима в другой показан на рис. 13. Стрелками указана последовательность появления выходных сигналов триггера при подаче единичных сигналов на S- и R-входы в режимах записи О и 1, а пунктирными линиями - неопределённые (случайные) значения (или 0, или 1) хранимой информации после перехода триггера из запрещённого режима (7-й такт) в режим хранения (8-й. . .10-й такты).

Переход RS -триггера из одного режима в другой показан на рис. 13. Стрелками указана последовательность появления выходных сигналов триггера при подаче единичных сигналов на S- и R-входы в режимах записи О и 1, а пунктирными линиями - неопределённые (случайные) значения (или 0, или 1) хранимой информации после перехода триггера из запрещённого режима (7-й такт) в режим хранения (8-й. . .10-й такты).

Возможность перехода RS -триггера в случайное состояние при выходе из запрещённого режима работы является крупным его недостатком. Поэтому в последовательностных Л. с. используются, как правило, сложные триггеры, у к-рых нет запрещённых режимов работы. Любой тип сложного триггера состоит из базовой ячейки памяти RS -триггера) и устройства управления, к-рое представляет собой Л. с., преобразующую входную информацию в R- и S-сигналы.

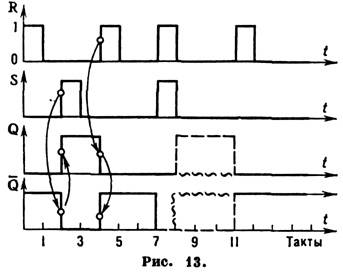

Простейшую схему управления имеет статич. D -триггер (рис. 14, а). Его управляющее устройство - комбинац. схема, состоящая из инвертора и двух ЛЭ И. Сигналы, предназначенные для записи, поступают на вход D. На вход синхронизации С подаются тактовые импульсы (синхроимпульсы), определяющие момент записи. Как видно из рис. 14, a, S=D*C, a R =

Следовательно, при С=0 независимо от значения D имеем S=R=0, т. е. RS -триггер находится в режиме хранения информации. При С=1 либо S-, либо R-сигнал равен 1 и триггер находится в режиме записи единицы (при D = l) или нуля (при D=0). Сигнал на выходе Q может измениться только в первой части каждого такта, пока на входе С имеется сигнал единичного уровня (рис. 14, б). Во второй части такта (при С=0) триггер находится в режиме хранения информации, и поэтому выходной сигнал задерживается до окончания того такта, в к-ром он был записан. Так, единичный сигнал на входе D заканчивается задолго до конца 0-го и 3-го тактов, а на выходе триггера он задерживается до начала 1-го и 4-го тактов. Недостатком статич. D-триггера является сквозная передача информации с D-входа на выход во время действия синхроимпульса, в результате чего сигнал на выходе триггера может измениться неск. раз в пределах одного такта (напр., 2-й такт, рис. 14, б).

Следовательно, при С=0 независимо от значения D имеем S=R=0, т. е. RS -триггер находится в режиме хранения информации. При С=1 либо S-, либо R-сигнал равен 1 и триггер находится в режиме записи единицы (при D = l) или нуля (при D=0). Сигнал на выходе Q может измениться только в первой части каждого такта, пока на входе С имеется сигнал единичного уровня (рис. 14, б). Во второй части такта (при С=0) триггер находится в режиме хранения информации, и поэтому выходной сигнал задерживается до окончания того такта, в к-ром он был записан. Так, единичный сигнал на входе D заканчивается задолго до конца 0-го и 3-го тактов, а на выходе триггера он задерживается до начала 1-го и 4-го тактов. Недостатком статич. D-триггера является сквозная передача информации с D-входа на выход во время действия синхроимпульса, в результате чего сигнал на выходе триггера может измениться неск. раз в пределах одного такта (напр., 2-й такт, рис. 14, б).

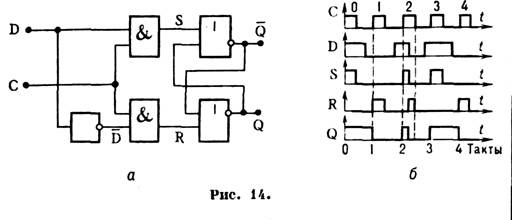

В динамич. D-триггере, свободном от недостатков статич. Д-триггера, запись информации производится только во время одного изперепадов напряжения (или из 0 в 1, или из 1 в 0) на входе С, и поэтому выходной сигнал может измениться только один раз в пределах такта [2]. Условно-графич. обозначение одного из динамич. D -триггеров см. на рис. 15.

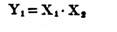

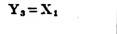

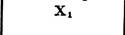

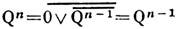

Соединив в динамич. D -триггере инверсный выход

с информац. входом D (рис. 16, а), получают счётный T -триггер, к-рый имеет только один управляющий вход Т (рис. 16, б). Первоначально на выходе Q этого триггера - нулевой сигнал (рис. 16, в), а на входе D=

с информац. входом D (рис. 16, а), получают счётный T -триггер, к-рый имеет только один управляющий вход Т (рис. 16, б). Первоначально на выходе Q этого триггера - нулевой сигнал (рис. 16, в), а на входе D= =1. По фронту первого синхроимпульса единичное состояние с D-входа перепишется на выход Q и соответственно на выходе

=1. По фронту первого синхроимпульса единичное состояние с D-входа перепишется на выход Q и соответственно на выходе  и входе D появится нуль. В след. такте на D-выход будет переписан нулевой сигнал с D-входа. Т. о., информация на выходе T -триггера будет меняться на противоположную по приходу каждого счётного синхроимпульса, а число выходных импульсов уменьшится в два раза по сравнению с числом входных импульсов.

и входе D появится нуль. В след. такте на D-выход будет переписан нулевой сигнал с D-входа. Т. о., информация на выходе T -триггера будет меняться на противоположную по приходу каждого счётного синхроимпульса, а число выходных импульсов уменьшится в два раза по сравнению с числом входных импульсов.

Регистр - последовательностный ОЭ, предназначенный для хранения и (или) преобразования многоразрядных двоичных чисел. Регистр состоит из набора триггеров, число к-рых равно макс. разрядности хранимых чисел.

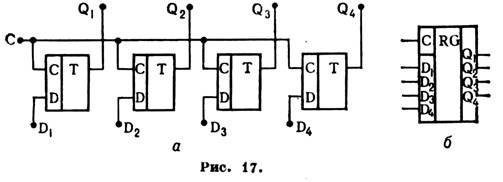

Простейший регистр - регистр с параллельным вводом информации. Схему и условно-графич. обозначение 4-разрядного регистра на D-триггерах см. на рис. 17.

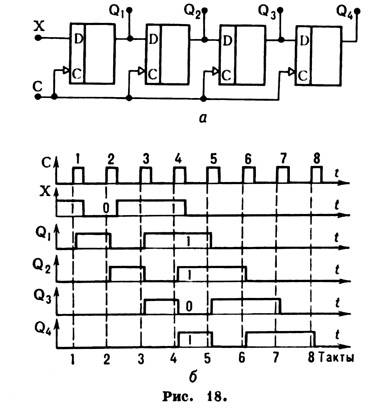

Параллельный двоичный 4-разрядный код поступает на информац. входы D1, . . ., D4 всех триггеров и записывается в регистр по приходу синхроимпульса С. В промежутках между синхроимпульсами происходит подготовка новой входной информации, а её смена в регистре осуществляется по очередному синхроимпульсу. Такие регистры в основном используются в системах оперативной памяти (см. Памяти устройства). Схема регистра с последоват. вводом информации, выполненного на D-триггерах с динамич. управлением, и его временные диаграммы см. на рис. 18. По приходу синхроимпульса С в первый триггер записывается код (О или 1), находящийся в этот момент на его D-входе. Каждый следующий триггер по этому же синхроимпульсу переключается в состояние, в к-ром в этот момент находился предыдущий триггер. Это происходит потому, что выходное состояние триггера изменяется с нек-рой задержкой относительно фронта синхроимпульса, равной времени срабатывания триггера (рис. 18, б). Следовательно, при последоват. соединении триггеров каждый синхроимпульс сдвигает код числа в регистре на один разряд, и поэтому для записи n -разрядного кода требуется п синхроимпульсов. Напр., в регистр вводится двоичный 4-разрядный код 1011 (рис. 18, б). По 1-му синхроимпульсу в 1-й триггер записывается единица старшего разряда. По 2-му синхроимпульсу эта единица перепишется с выхода 1-го на выход 2-го триггера, а в 1-й триггер запишется нуль (следующий разряд кода). Таким же образом после прихода 4-го синхроимпульса в регистре окажется записанным число Q4-1. Q3-0, Q2-1. Q1-1. Дo прихода след. импульса последовательно введённый 4-разрядный код будет храниться в регистре в виде параллельного кода, к-рый можно считывать с выходов Q4, . . ., Q1.

Большое распространение получили универсальные регистры [2; 4], способные записывать и считывать числа как в последовательном, так и в параллельном кодах. Поэтому их можно использовать для преобразования последоват. кода в параллельный и наоборот, выполнения нек-рых арифметич. и логич. операций. Благодаря своей многофункциональности регистры стали одними из наиболее распространённых ОЭ в системах автоматики и вычислит. техники.

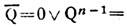

Счётчик - последовательностный ОЭ, предназначенный для счёта импульсов, поступивших на его вход. Счётчик состоит из цепочки триггеров, число к-рых определяет его разрядность, а следовательно, и число разл. состояний счётчика, к-рое наз. коэф. (модулем) счёта - К. Если кол-во входных импульсов больше модуля счёта, то через каждые К импульсов счётчик возвращается в исходное состояние и цикл счёта начинается сначала.

Простейшим одноразрядным счётчиком с К=2 является одиночный T -триггер, меняющий своё состояние на противоположное под действием каждого входного импульса. Если за нач. состояние триггера принять Q=0, то по приходу 1-го импульса он перейдёт в новое состояние с Q = l, а при поступлении 2-го импульса снова вернётся в исходное состояние с Q=0 и счёт может начинаться сначала. Цепочка из т счётных триггеров образует последоват. m -разрядный двоичный счётчик. Результат счёта отображается на выходах всех триггеров Qm,....,Q1 в виде параллельного двоичного кода числа сосчитанных импульсов, к-рый может принимать значения от 0, . . ., О до 1, . . ., 1. Т. к. число разрядов равно т, а каждая переменная может принимать лишь два значения (0 или 1), то число возможных состояний К=2m. Макс. число импульсов, при к-ром счётчик полностью заполняется единицами, равно (2m-1), т. к. с приходом 2m -го импульса счётчик опять переходит в нулевое состояние.

На рис. 19, а приведена схема 4-разрядного двоичного счётчика на T -триггерах, срабатывающих по заднему фронту при переходе из 1 в 0 входного сигнала. Условно-графич. обозначение счётчика и его временные диаграммы см. на рис. 19, б. Диаграммы начинаются с момента, когда счётчик заполнен, т. е. на всех его выходах находятся сигналы единичного уровня - 1111. Число импульсов, подсчитанных счётчиком к этому времени, 11112=1*23+1*22+1*21+1*20=15, что соответствует последнему (24-1) его состоянию. По заднему фронту следующего (16-го) импульса все триггеры последовательно переключаются (стрелки на диаграмме) и счётчик переходит в исходное (нулевое) состояние. С приходом каждого след. импульса параллельный двоичный код на выходе счётчика будет увеличиваться на единицу, пока снова не наступит переполнение счётчика.

Рассмотренный суммирующий счётчик можно преобразовать в вычитающий, у к-рого выходной код будет уменьшаться на единицу с приходом каждого счётного импульса. Для этого достаточно входы синхронизации 2-го и следующих триггеров подключить не к прямым, а к инверсным

выходам предыдущих триггеров.

выходам предыдущих триггеров.

Наиб. часто используются счётчики с коэф. счёта, не равным 2m. Напр., в электронных часах необходимы счётчики с модулем К=6(десятки мин), K = 10 (единицы мин), К=7(дни недели). Для построения счётчика с

можно использовать цепочку из т триггеров, для к-рой выполняется условие

можно использовать цепочку из т триггеров, для к-рой выполняется условие  Очевидно, такой счётчик имеет лишние устойчивые состояния (2m- - К). Их исключают, вводя обратные связи в цепь сброса счётчика в нулевое состояние, в том такте работы, когда счётчик досчитывает до числа К. Напр., для счётчика с K=5 нужны три триггера, т. к.

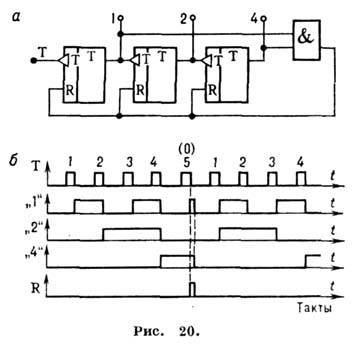

Очевидно, такой счётчик имеет лишние устойчивые состояния (2m- - К). Их исключают, вводя обратные связи в цепь сброса счётчика в нулевое состояние, в том такте работы, когда счётчик досчитывает до числа К. Напр., для счётчика с K=5 нужны три триггера, т. к. Счётчик должен иметь пять устойчивых состояний N=0, 1, 2, 3, 4. В том такте, когда он должен перейти в устойчивое состояние N=5, его необходимо установить в исходное нулевое состояние. В схему такого счётчика (рис. 20, а) помимо трёх триггеров включают логич. элемент И, на к-рый подают выходные сигналы счётчика, соответствующие первому запрещённому состоянию, т. е. числу 5. С выхода элемента И сигнал сброса поступает на входы установки триггеров в 0 (R-входы). Как видно из диаграммы (рис. 20, б), в самом начале 6-го состояния (число 5) на обоих входах элемента И появляются логич. 1, вызывающие появление сигнала R = l, сбрасывающего счётчик в исходное состояние. После сброса триггера в нуль исчезает и единичный R-сигнал в цепи обратной связи и счётчик снова готов к работе в новом цикле.

Счётчик должен иметь пять устойчивых состояний N=0, 1, 2, 3, 4. В том такте, когда он должен перейти в устойчивое состояние N=5, его необходимо установить в исходное нулевое состояние. В схему такого счётчика (рис. 20, а) помимо трёх триггеров включают логич. элемент И, на к-рый подают выходные сигналы счётчика, соответствующие первому запрещённому состоянию, т. е. числу 5. С выхода элемента И сигнал сброса поступает на входы установки триггеров в 0 (R-входы). Как видно из диаграммы (рис. 20, б), в самом начале 6-го состояния (число 5) на обоих входах элемента И появляются логич. 1, вызывающие появление сигнала R = l, сбрасывающего счётчик в исходное состояние. После сброса триггера в нуль исчезает и единичный R-сигнал в цепи обратной связи и счётчик снова готов к работе в новом цикле.

Счётчики могут выполнять ф-ции делителей частоты, т. е. устройств, формирующих из импульсной последовательности с частотой f вх, импульсную последовательность f вых

на выходе последнего триггера с частотой

на выходе последнего триггера с частотой

Помимо рассмотренных простейших типов счётчиков существует большое кол-во более совершенных, но и значительно более сложных конструкций, обладающих лучшими параметрами и дополнит. функциональными возможностями [2, 4].

Осн. типы Л. с. являются базой для построения разнообразных цифровых устройств ( процессоров, памяти устройств и пр.), из к-рых состоят совр. ЭВМ и системы автоматич. управления объектами и процессами.

Лит.:1) Савельев А. Я., Арифметические и логические основы цифровых автоматов, М., 1980; 2) Зельдин Е. А., Цифровые интегральные микросхемы в информационно-измерительной аппаратуре, Л., 1986; 3) 3алманзон Л. А., Беседы об автоматике и кибернетике, М., 1981; 4) Мальцева Л. А., Фромберг Э. М., Ямпольский В. С., Основы цифровой техники, М., 1986; 5) ГОСТ 2. 743-82. Обозначения условные графические в схемах. Элементы цифровой техники. В. С. Ямполъский.

Физическая энциклопедия. В 5-ти томах. — М.: Советская энциклопедия. Главный редактор А. М. Прохоров. 1988.

.