- SRAM (память)

-

Типы компьютерной памяти Энергозависимая - DRAM (в том числе DDR SDRAM)

- SRAM

- Перспективные

- T-RAM

- Z-RAM

- TTRAM

- Из истории

- Память на линиях задержки

- Запоминающая электронстатическая трубка

- Запоминающая ЭЛТ

Энергонезависимая - ПЗУ

- Первые разработки

- Перспективные

- Из истории

- Магнитный барабан

- Память на магнитных сердечниках

- Память на магнитной проволоке

- Пузырьковая память

- Память на твисторах

Статическая оперативная память с произвольным доступом (SRAM, static random access memory) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM). Тем не менее, сохранять данные без перезаписи SRAM может только пока есть питание, то есть SRAM остается энергозависимым типом памяти. Произвольный доступ (RAM — random access memory) — возможность выбирать для записи/чтения любой из битов (тритов) (чаще байтов (трайтов), зависит от особенностей конструкции), в отличие от памяти с последовательным доступом (SAM — sequential access memory).

Содержание

Двоичная SRAM

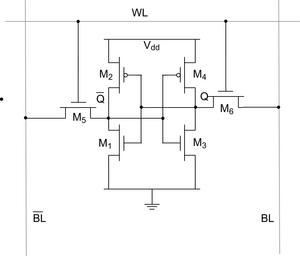

Рис. 1. Шеститранзисторная ячейка статической двоичной памяти (бит) SRAM

Рис. 1. Шеститранзисторная ячейка статической двоичной памяти (бит) SRAM

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых транзисторов для обеспечения доступа к ячейке (рис. 1.). Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы. Недостатком такого решения является рост статического энергопотребления.

Линия WL (Word Line) управляет двумя транзисторами доступа. Линии BL и BL (Bit Line) — битовые линии, используются и для записи данных и для чтения данных.

Запись. При подаче «0» на линию BL или BL параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы 2ИЛИ, последующая подача «1» на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

Чтение. При подаче «1» на линию WL открываются транзисторы M5 и M6, уровни записанные в триггере выставляются на линии BL и BL и попадают на схемы чтения.

Восьмитранзисторная ячейка двоичной SRAM описана в [1].

Переключение триггеров через транзисторы доступа является неявной логической функцией приоритетного переключения, которая в явном виде, для двоичных триггеров, строится на двухвходовых логических элементах 2ИЛИ-НЕ или 2И-НЕ. Схема ячейки с явным переключением является обычным RS-триггером. При явной схеме переключения линии чтения и записи разделяются, отпадает нужда в транзисторах доступа в схеме записи-чтения с неявным приоритетом(по 2 транзистора на 1 ячейку), но появляется нужда в схемах записи-чтения с явным приоритетом.

В настоящее время появилась усовершенствованная схема [2] с обратной связью отключаемой сигналом записи, которая не требует транзисторов нагрузки и соответственно избавлена от высокого потребления энергии при записи.

Троичная SRAM

Возможно, эта статья содержит оригинальное исследование. Добавьте ссылки на источники, в противном случае она может быть выставлена на удаление.

Дополнительные сведения могут быть на странице обсуждения. (25 мая 2011)Проверить информацию. Необходимо проверить точность фактов и достоверность сведений, изложенных в этой статье.

На странице обсуждения должны быть пояснения.Проект троичной SRAM на трёхразрядных однозначных троичных триггерах описан в [3].

Один логический элемент 2ИЛИ-НЕ состоит из двух двухзатворных транзисторов (четырёх однозатворных), три — из шести (двенадцати однозатворных), плюс три транзистора доступа, всего — девять транзисторов (пятнадцать) на одну трёхбитную ячейку памяти (трит).

Преимущества

- Быстрый доступ. SRAM — это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

- Простая схемотехника — SRAM не требуются сложные контроллеры.

- Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

- Низкое энергопотребление.

Недостатки

- Невысокая плотность записи (шесть-восемь элементов на бит[4], вместо двух у DRAM).

- Вследствие чего — дороговизна килобайта памяти.

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора. Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

SRAM применяется в микроконтроллерах и ПЛИС, в которых объём ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счёт отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

В устройствах с большим объёмом ОЗУ рабочая память выполняется как DRAM. SRAM’ом же делают регистры и кеш-память.

См. также

Примечания

- ↑ http://www.citforum.ru/book/optimize/sdram.shtml Принципы функционирования SRAM. Крис Касперски

- ↑ http://timeinventor.com/news.php?readmore=118 D-триггер или ячейка регистра/памяти

- ↑ Троичная SRAM

- ↑ Компания MoSys продаёт DRAM со встроенным контроллером под маркой 1T-SRAM, но это, естественно, не делает её SRAM’ом.

Это заготовка статьи о компьютерах. Вы можете помочь проекту, исправив и дополнив её.

Это примечание по возможности следует заменить более точным.Микроконтроллеры Архитектура 8-бит MCS-51 • MCS-48 • PIC • AVR • Z8 • H8 • COP8 • 68HC08 • 68HC11 16-бит MSP430 • MCS-96 • MCS-296 • PIC24 • MAXQ • Nios • 68HC12 • 68HC16 32-бит ARM • MIPS • AVR32 • PIC32 • 683XX • M32R • SuperH • Nios II • Am29000 • LatticeMico32 • MPC5xx • PowerQUICC • Parallax Propeller Производители Analog Devices • Atmel • Silabs • Freescale • Fujitsu • Holtek • Hynix • Infineon • Intel • Microchip • Maxim • Parallax • NXP Semiconductors • Renesas • Texas Instruments • Toshiba • Ubicom • Zilog • Cypress Компоненты Регистр • Процессор • SRAM • EEPROM • Флеш-память • Кварцевый резонатор • Кварцевый генератор • RC-генератор • Корпус Периферия Таймер • АЦП • ЦАП • Компаратор • ШИМ-контроллер • Счётчик • LCD • Датчик температуры • Watchdog Timer Интерфейсы CAN • UART • USB • SPI • I²C • Ethernet • 1-Wire ОС FreeRTOS • μClinux • BeRTOS • ChibiOS/RT • eCos • RTEMS • Unison • MicroC/OS-II • Nucleus Программирование JTAG • C2 • Программатор • Ассемблер • Прерывание • MPLAB • AVR Studio • MCStudio Категория:- Оперативная память

Wikimedia Foundation. 2010.