- Программируемая пользователем вентильная матрица

-

ППВМ типа Stratix IV GX фирмы Altera

ППВМ типа Stratix IV GX фирмы Altera

Программи́руемая по́льзователем ве́нтильная ма́трица (ППВМ, FPGA) — полупроводниковое устройство, которое может быть сконфигурировано производителем или разработчиком после изготовления; отсюда название: «программируемая пользователем». ППВМ программируются путём изменения логики работы принципиальной схемы, например, с помощью исходного кода на языке проектирования (типа VHDL), на котором можно описать эту логику работы микросхемы. ППВМ является одной из архитектурных разновидностей программируемых логических интегральных схем (ПЛИС).

ППВМ могут быть модифицированы практически в любой момент в процессе их использования. Они состоят из конфигурируемых логических блоков, подобных переключателям с множеством входов и одним выходом (логические вентили или gates). В цифровых схемах такие переключатели реализуют базовые двоичные операции AND, NAND, OR, NOR и XOR. В большинстве современных микропроцессоров функции логических блоков фиксированы и не могут модифицироваться. Принципиальное отличие ППВМ состоит в том, что и функции блоков, и конфигурация соединений между ними могут меняться с помощью специальных сигналов, посылаемых схеме. В некоторых специализированных интегральных схемах (ASIC) используются логические матрицы, аналогичные ППВМ по структуре, однако они конфигурируются один раз в процессе производства, в то время как ППВМ могут постоянно перепрограммироваться и менять топологию соединений в процессе использования. Однако, такая гибкость требует существенного увеличения количества транзисторов микросхемы.

Содержание

История

Индустрия ППВМ выросла из программируемых ПЗУ (ППЗУ) и программируемых логических интегральных схем (ПЛИС). Оба эти типа устройств являются программируемыми, причём программирование может выполняться либо на заводе-изготовителе, либо пользователем, однако, программирование их работы состоит только в изменении связей между вентилями.[1] Сооснователи Xilinx Росс Фримен (англ.)русск. и Бернард Вандершмит (англ.)русск. изобрели первую коммерчески пригодную ППВМ XC2064 в 1985 году. Эта микросхема, имеющая программируемые вентили и программируемые соединения между вентилями, положила начало новой технологии и новому рынку. Через 20 лет за это изобретение Росс Фримен был занесён в Национальный Зал славы изобретателей США (англ.)русск..

Сама концепция программируемых вентильных матриц, логических вентилей и логических блоков запатентована Дэвидом Пейджем и Луверном Петерсоном в 1985 году.[2][3] В 1990-х годах произошёл резкий скачок интереса к ППВМ, возросла их сложность и объёмы производства. Если в начале 1990-х годов ППВМ использовались в основном в области телекоммуникаций и сетей связи, то к концу десятилетия они нашли своё применение в потребительских товарах, в автомобильной промышленности и других отраслях.

Всплеск славы ППВМ произошёл в 1997 году, когда Адриан Томпсон объединил генетические алгоритмы и технологию ППВМ для создания устройства, способного отличать тоны частотой 1 КГц и 10 КГц. Генетические алгоритмы позволили с помощью вентильной матрицы размером 64 х 64 клеток на чипе фирмы Xilinx создать конфигурацию, необходимую для решения поставленной задачи.[4]

Архитектура

ППВМ включают в себя три главных программируемых элемента: нескоммутированные программируемые логические блоки (ПЛБ), блоки ввода-вывода (БВВ) и внутренние связи. ПЛБ являются функциональными элементами для построения логики пользователя, БВВ обеспечивают связь между контактами корпуса и внутренними сигнальными линиями. Программируемые ресурсы внутренних связей обеспечивают управление путями соединения входов и выходов ПЛБ и блоков ввода-вывода на соответствующие сети.[5] Все каналы трассировки имеют одинаковую ширину (одинаковое количество проводников). Большинство блоков БВВ вписываются либо в одну строку (по высоте), либо в один столбец (по ширине) массива вентилей.

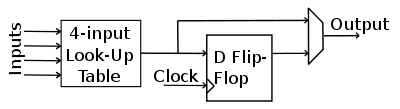

Логический блок классической ППВМ состоит из таблицы поиска на 4 входа и триггера (см. рисунок ниже). В последние годы производители начали переходить на таблицы поиска с 6 входами в высокопроизводительных частях схемы, объясняя это необходимостью повышения производительности.[6]

Логический блок имеет таблицу поиска на 4 входа и вход синхронизации (clock). Выход блока только один, это может быть регистровая или нерегистровая выходная таблица поиска. Поскольку сигналы синхронизации в коммерческих ППВМ (а часто и другие сигналы, распараллеливающиеся на большое количество входов — high-fanout signals) трассируются особым образом специальными трассировочными цепями, управление этими сигналами делается отдельно.

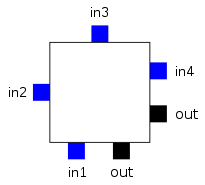

Для приведённого примера архитектуры расположение контактов логического блока показано ниже.

Входы расположены на отдельных сторонах логического блока, выходной контакт может трассироваться в двух каналах: либо справа от блока, либо снизу. Выходные контакты каждого логического блока могут соединяться с трассировочными сегментами в смежных каналах. Аналогично, контактная площадка блока ввода-вывода (pad) может соединяться с трассировочным элементом в любом смежном канале. Например, верхняя контактная площадка чипа может соединяться с любым из W проводников (где W - ширина канала) в горизонтальном канале, расположенном непосредственно под ним.

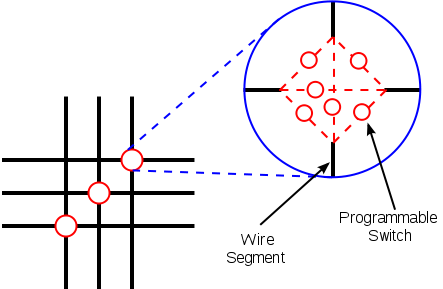

Как правило, трассировка ППВМ несегментирована, то есть каждый сегмент проводника соединяет только один логический блок с переключательным блоком. Из-за огибания программируемых переключателей в переключательном блоке трассировка получается более длинной. Для увеличения скорости внутрисистемных соединений, в некоторых архитектурах ППВМ используются более длинные трассировочные соединения между логическими блоками.

В месте пересечения вертикальных и горизонтальных каналов создаются переключательные блоки. При такой архитектуре для каждого проводника, входящего в переключательный блок, существуют три программируемых переключателя, которые позволяют ему подключаться к трём другим проводникам в смежных сегментах канала. Модель или топология выключателей, используемая в этой архитектуры, является планарной или доменной топологией переключательных блоков. В этой топологии проводник трассы номер один подключается только к проводнику трассы номер один в смежных каналах, проводник трассы номер 2 подключается только к проводникам трассы номер 2 и так далее. На рисунке ниже показаны соединения в переключательном блоке.

Современные семейства ППВМ расширяют перечисленные выше возможности и включают встроенную функциональность высокого уровня. Имея эти общие функции, встроенные в кремний, можно сократить площадь кристалла, к тому же эти функции будут работать быстрее, чем если их создавать на базе примитивов. Примерами таких функций являются мультиплексоры, блоки цифровой обработки сигналов, встроенные процессоры, быстрая логика ввода-вывода и встроенная память.

ППВМ также широко применяются для систем проверки пригодности, в том числе в докремниевой и послекремниевой проверке пригодности, а также при разработке встроенных программ. Это позволяет компаниям-производителям интегральных схем проверять работоспособность своих устройств до изготовления их на заводе, сокращая время выхода изделия на рынок.

Производители

Основными производителями ППВМ являются:

См. также

Примечания

- ↑ History of FPGAs (англ.)

- ↑ Google Patent Search, "Re-programmable PLA".

- ↑ Google Patent Search, "Dynamic data re-programmable PLA".

- ↑ On the Origin of Circuits.

- ↑ Архитектура FPGA (англ.)

- ↑ Achieving Higher System Performance with the Virtex-5 Family of FPGA, WP245 (v1.1.1) July 7, 2006 xilinx.com (англ.)

Ссылки

- History of the programmable logic (англ.)

- Конфигурируемые процессоры

- Методология высокоуровневого проектирования устройств на базе FPGA

- ПЛИС с архитектурой FPGA семейства Virtex

Технологии цифровых процессоров Архитектура CISC · EDGE · EPIC · MISC · URISC · RISC · VLIW · ZISC · Фон Неймана · Гарвардская

8 бит · 16 бит · 32 бит · 64 бит · 128 битПараллелизм Pipeline Конвейер · In-Order & Out-of-Order execution · Переименование регистров · Speculative execution Уровни Бит · Инструкций · Суперскалярность · Данных · Задач Потоки Многопоточность · Simultaneous multithreading · Hyperthreading · Superthreading · Аппаратная виртуализация Классификация Флинна SISD · SIMD · MISD · MIMD Реализации DSP · GPU · SoC · PPU · Векторный процессор · Математический сопроцессор • Микропроцессор · Микроконтроллер Компоненты Barrel shifter · FPU · BSB · MMU · TLB · Регистровый файл · control unit · АЛУ • Демультиплексор · Мультиплексор · Микрокод · Тактовая частота • Корпус • Регистры • Кэш (Кэш процессора) Управление питанием APM · ACPI · Clock gating · Динамическое изменение частоты • Динамическое изменение напряжения Категории:- Технологии процессоров

- Вентильные матрицы

Wikimedia Foundation. 2010.